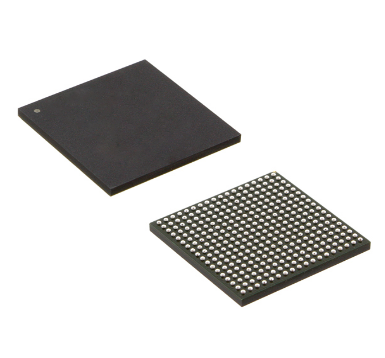

The XC6SLX25T-N3CSG324I Spartan-6 FPGA has up to six CMTs, each consisting of two DCMs and one PLL, and can be used alone or in a cascade. The Spartan-6 FPGA extends the density of 3840 to 147443 logic units, with only half the power consumption of the previous Spartan series, and has faster and more comprehensive connectivity. The Spartan-6 series adopts mature 45 nanometer low-power copper process technology, achieving the best balance of cost, power consumption, and performance, providing a new and more efficient dual register 6-input lookup table logic and rich built-in system level blocks.

The XC6SLX25T-N3CSG324I Spartan-6 FPGA has up to six CMTs, each consisting of two DCMs and one PLL, and can be used alone or in a cascade. The Spartan-6 FPGA extends the density of 3840 to 147443 logic units, with only half the power consumption of the previous Spartan series, and has faster and more comprehensive connectivity. The Spartan-6 series adopts mature 45 nanometer low-power copper process technology, achieving the best balance of cost, power consumption, and performance, providing a new and more efficient dual register 6-input lookup table logic and rich built-in system level blocks.

characteristic

Multiple efficient integrated blocks

Optimized I/O standard selection

Staggered solder pads

Large scale plastic wire key packaging

45 nanometer process optimized for cost and low power consumption

Sleep power-off mode, achieving zero power consumption

Each differential I/O has a data transfer rate of up to 1080 Mb/s

Optional output driver, up to 24 mA per pin

3.3V to 1.2V I/O standards and protocols

Low cost HSTL and SSTL memory interfaces

Compliant with hot swappable standards

Adjustable I/O conversion rate to improve signal integrity

Integrated endpoint module for PCI Express design

High performance arithmetic and signal processing

Fast 18 x 18 multiplier and 48 bit accumulator

Pipeline and cascading functions

Pre encoder for auxiliary filter applications